University of Illinois at Urbana-Champaign Dept. of Electrical and Computer Engineering

ECE 120: Introduction to Computing

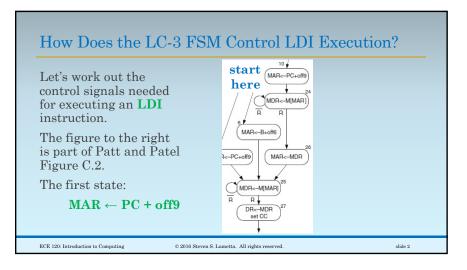

LC-3 Control Signals for Execution of an LDI

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 1

slide 3

#### What are the Load Signals?

$MAR \leftarrow PC + off9$

Which registers change?

|      | LD.<br>MAR | LD.<br>MDR |   |   | LD.<br>REG |   |   |

|------|------------|------------|---|---|------------|---|---|

| LDI1 | 1          | 0          | 0 | 0 | 0          | 0 | 0 |

| LDI2 |            |            |   |   |            |   |   |

| LDI3 |            |            |   |   |            |   |   |

| LDI4 |            |            |   |   |            |   |   |

| LDI5 |            |            |   |   |            |   |   |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

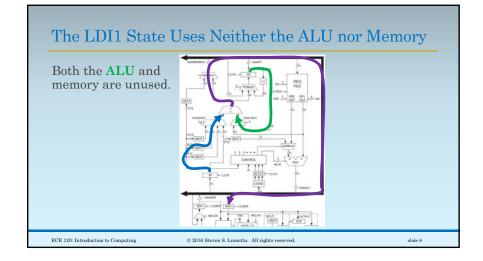

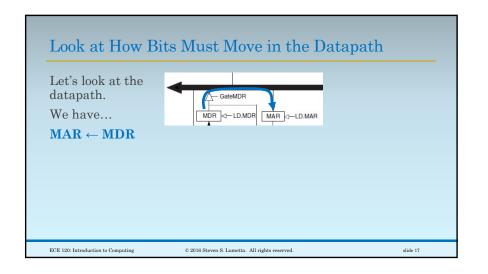

Look at How Bits Must Move in the Datapath

Let's look at the datapath.

We have...

MAR ← PC + off9

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

#### What are the Bus Gating Signals?

$MAR \leftarrow PC + off9$

So what are the bus gating signals?

|      | GatePC | GateMDR | GateALU | Gate<br>MARMUX |

|------|--------|---------|---------|----------------|

| LDI1 | 0      | 0       | 0       | 1              |

| LDI2 |        |         |         |                |

| LDI3 |        |         |         |                |

| LDI4 |        |         |         |                |

| LDI5 |        |         |         |                |

ECE 120: Introduction to Computing

$\mathbb C$  2016 Steven S. Lumetta. All rights reserved.

slide 5

slide 7

Which Muxes are Needed for LDI1?

Which muxes matter?

The three address generation muxes (ADDR1MUX, ADDR2MUX, and MARMUX).

ECE 120: Introduction to Computing

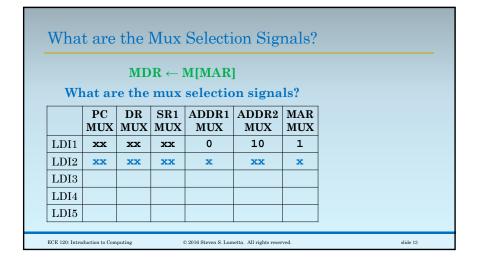

## What are the Mux Selection Signals?

$MAR \leftarrow PC + off9$

What are the mux selection signals?

|      | PC<br>MUX | DR<br>MUX | SR1<br>MUX |   | ADDR2<br>MUX | MAR<br>MUX |

|------|-----------|-----------|------------|---|--------------|------------|

| LDI1 | xx        | xx        | xx         | 0 | 10           | 1          |

| LDI2 |           |           |            |   |              |            |

| LDI3 |           |           |            |   |              |            |

| LDI4 |           |           |            |   |              |            |

| LDI5 |           |           |            |   |              |            |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

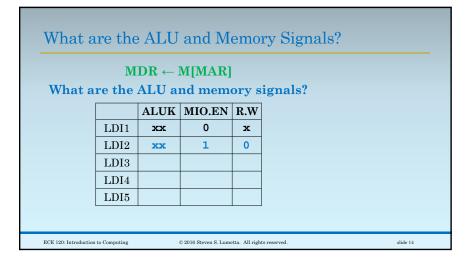

## What are the ALU and Memory Signals?

$MAR \leftarrow PC \text{+ off9}$  What are the ALU and memory signals?

|      | ALUK | MIO.EN | R.W |

|------|------|--------|-----|

| LDI1 | xx   | 0      | x   |

| LDI2 |      |        |     |

| LDI3 |      |        |     |

| LDI4 |      |        |     |

| LDI5 |      |        |     |

ECE 120: Introduction to Computing

$\ensuremath{\mathbb{C}}$  2016 Steven S. Lumetta. All rights reserved.

slide 9

slide 11

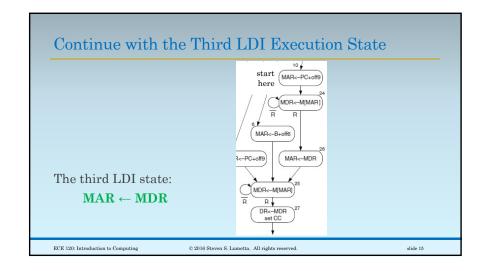

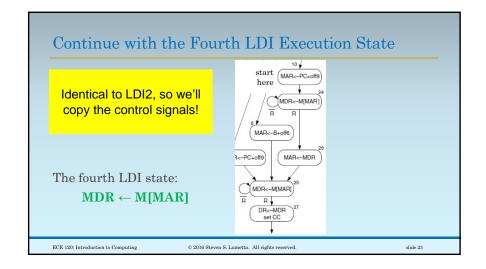

Continue with the Second LDI Execution State start MAR<-PC+off9 Identical to the second fetch state's RTL, so we'll MDR -M[MAR] copy the control signals! MAR<-B+off6 MAR<-MDR R<-PC+off9 The second LDI state: MDR<-M[MAR]  $MDR \leftarrow M[MAR]$ DR<-MDR ECE 120: Introduction to Computing © 2016 Steven S. Lumetta. All rights reserved. slide 10

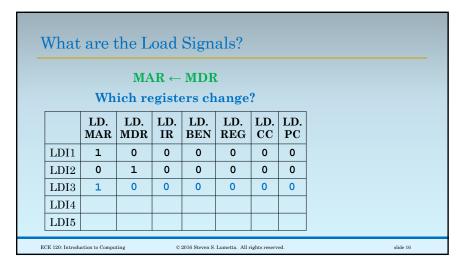

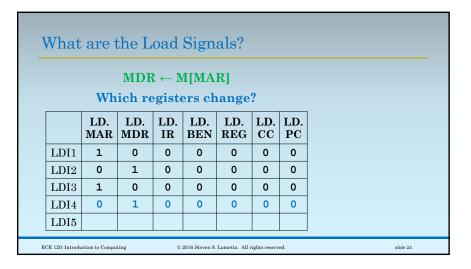

#### What are the Load Signals?

$MDR \leftarrow M[MAR]$

Which registers change?

|      | LD.<br>MAR | LD.<br>MDR |   | LD.<br>BEN | LD.<br>REG |   | LD.<br>PC |

|------|------------|------------|---|------------|------------|---|-----------|

| LDI1 | 1          | 0          | 0 | 0          | 0          | 0 | 0         |

| LDI2 | 0          | 1          | 0 | 0          | 0          | 0 | 0         |

| LDI3 |            |            |   |            |            |   |           |

| LDI4 |            |            |   |            |            |   |           |

| LDI5 |            |            |   |            |            |   |           |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

What are the Bus Gating Signals?

$MDR \leftarrow M[MAR]$

What are the bus gating signals?

|    |    | GatePC | GateMDR | GateALU | Gate<br>MARMUX |

|----|----|--------|---------|---------|----------------|

| LD | Ι1 | 0      | 0       | 0       | 1              |

| LD | I2 | 0      | 0       | 0       | 0              |

| LD | I3 |        |         |         |                |

| LD | I4 |        |         |         |                |

| LD | I5 |        |         |         |                |

ECE 120: Introduction to Computing

$\ensuremath{\mathbb{C}}$  2016 Steven S. Lumetta. All rights reserved.

slide 12

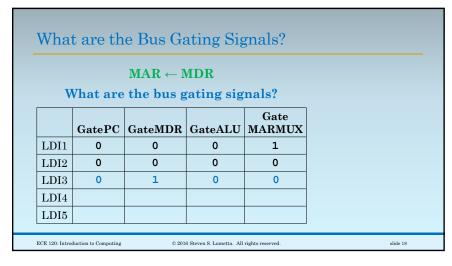

### What are the Bus Gating Signals?

$MDR \leftarrow M[MAR]$

What are the bus gating signals?

|      | GatePC | GateMDR | GateALU | Gate<br>MARMUX |

|------|--------|---------|---------|----------------|

| LDI1 | 0      | 0       | 0       | 1              |

| LDI2 | 0      | 0       | 0       | 0              |

| LDI3 | 0      | 1       | 0       | 0              |

| LDI4 | 0      | 0       | 0       | 0              |

| LDI5 |        |         |         |                |

ECE 120: Introduction to Computing

$\mathbb C$  2016 Steven S. Lumetta. All rights reserved.

slide 25

slide 27

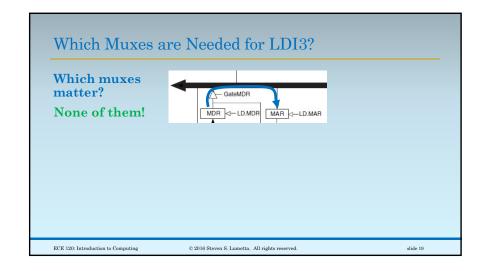

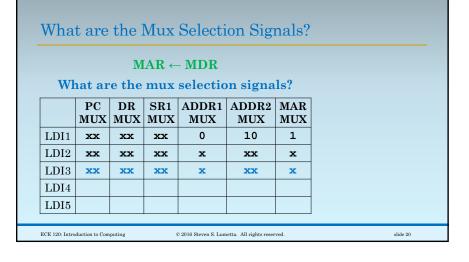

## What are the Mux Selection Signals?

$MDR \leftarrow M[MAR]$

What are the mux selection signals?

|   |      | PC  | DR  |     | ADDR1 |     |     |

|---|------|-----|-----|-----|-------|-----|-----|

|   |      | MUX | MUX | MUX | MUX   | MUX | MUX |

| ] | LDI1 | xx  | xx  | хх  | 0     | 10  | 1   |

| ] | LDI2 | xx  | xx  | xx  | x     | xx  | x   |

| ] | LDI3 | xx  | xx  | xx  | x     | xx  | x   |

| ] | LDI4 | xx  | xx  | xx  | x     | xx  | x   |

| ] | LDI5 |     |     |     |       |     |     |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 26

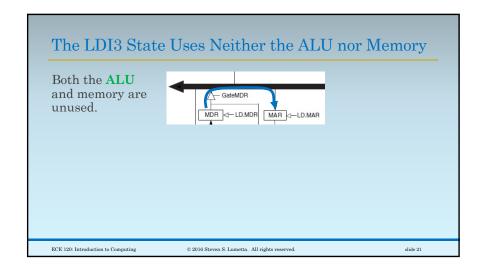

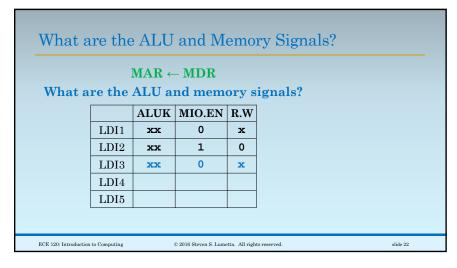

## What are the ALU and Memory Signals?

$MDR \leftarrow M[MAR]$

What are the ALU and memory signals?

|      | ALUK | MIO.EN | R.W |

|------|------|--------|-----|

| LDI1 | xx   | 0      | x   |

| LDI2 | xx   | 1      | 0   |

| LDI3 | xx   | 0      | x   |

| LDI4 | xx   | 1      | 0   |

| LDI5 |      |        |     |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

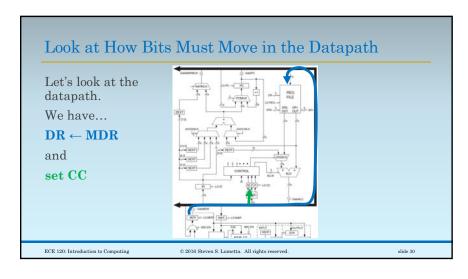

Continue with the Fifth LDI Execution State

| Start | MAR-PC+off9 |

| NAR-B+off6 |

| NAR-B+off

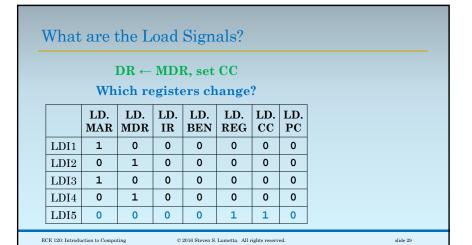

# What are the Bus Gating Signals?

$DR \leftarrow MDR$ , set CC What are the bus gating signals?

|      | GatePC | GateMDR | GateALU | Gate<br>MARMUX |

|------|--------|---------|---------|----------------|

| LDI1 | 0      | 0       | 0       | 1              |

| LDI2 | 0      | 0       | 0       | 0              |

| LDI3 | 0      | 1       | 0       | 0              |

| LDI4 | 0      | 0       | 0       | 0              |

| LDI5 | 0      | 1       | 0       | 0              |

© 2016 Steven S. Lumetta. All rights reserved.

ECE 120: Introduction to Computing

slide 31

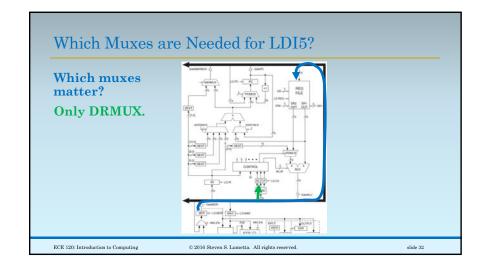

### What are the Mux Selection Signals?

$DR \leftarrow MDR$ , set CC

What are the mux selection signals?

|      | PC<br>MUX | DR<br>MUX |    | ADDR1<br>MUX | ADDR2<br>MUX | MAR<br>MUX |

|------|-----------|-----------|----|--------------|--------------|------------|

| LDI1 | xx        | xx        | xx | 0            | 10           | 1          |

| LDI2 | xx        | xx        | xx | x            | xx           | x          |

| LDI3 | xx        | xx        | xx | x            | xx           | x          |

| LDI4 | xx        | xx        | xx | x            | xx           | x          |

| LDI5 | xx        | 00        | xx | x            | xx           | x          |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 33

slide 35

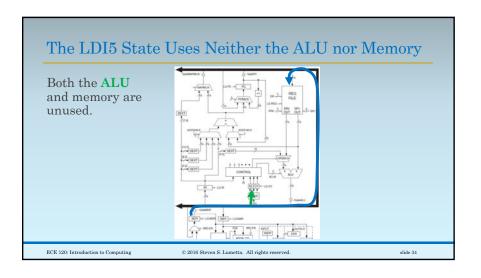

## What are the ALU and Memory Signals?

$\label{eq:DR} \begin{aligned} DR \leftarrow MDR, & set \ CC \\ What \ are \ the \ ALU \ and \ memory \ signals? \end{aligned}$

|      | ALUK | MIO.EN | R.W |

|------|------|--------|-----|

| LDI1 | xx   | 0      | x   |

| LDI2 | xx   | 1      | 0   |

| LDI3 | xx   | 0      | x   |

| LDI4 | xx   | 1      | 0   |

| LDI5 | xx   | 0      | x   |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

Summary of Control Signals for LDI Execution

|              | LD.<br>MAR | LD.<br>MDR | LD.<br>IR  | LD.<br>BEN | LD.<br>REG | LD.<br>CC           | LD.<br>PC |      | GatePC | GateMDR | GateA | LU I | Gate<br>MARMUX |     |

|--------------|------------|------------|------------|------------|------------|---------------------|-----------|------|--------|---------|-------|------|----------------|-----|

| LDI1         | 1          | 0          | 0          | 0          | 0          | 0                   | 0         | LDI1 | 0      | 0       | 0     |      | 1              |     |

| LDI2         | 0          | 1          | 0          | 0          | 0          | 0                   | 0         | LDI2 | 0      | 0       | 0     |      | 0              |     |

| LDI3         | 1          | 0          | 0          | 0          | 0          | 0                   | 0         | LDI3 | 0      | 1       | 0     |      | 0              |     |

| LDI4         | 0          | 1          | 0          | 0          | 0          | 0                   | 0         | LDI4 | 0      | 0       | 0     |      | 0              |     |

| LDI5         | 0          | 0          | 0          | 0          | 1          | 1                   | 0         | LDI5 | 0      | 1       | 0     |      | 0              |     |

|              | PC<br>MUX  | DR<br>MUX  | SR1<br>MUX | ADD<br>MU  |            | DDR2 MAR<br>MUX MUX |           |      |        |         | ALUK  | MIO. | EN I           | R.W |

| LDI1         | xx         | xx         | xx         | 0          |            | 10                  | 1         |      |        | LDI1    | xx    | 0    |                | x   |

| LDI2         | xx         | xx         | хx         | х          |            | хx                  | x         |      |        | LDI2    | xx    | 1    |                | 0   |

|              |            | xx         | xx         | x          |            | xx                  | ×         |      |        | LDI3    | xx    | 0    |                | x   |

| LDI3         | xx         | _ ^^       | 1 22       |            |            |                     |           |      |        |         |       |      |                |     |

| LDI3<br>LDI4 | xx         | xx         | xx         | ×          |            | xx                  | x         |      |        | LDI4    | xx    | 1    |                | 0   |