University of Illinois at Urbana-Champaign Dept. of Electrical and Computer Engineering

ECE 120: Introduction to Computing

Another Example of Serialization: Power-of-2 Checker

ECE 120: Introduction to Computing

$\ensuremath{\mathbb{C}}$  2016 Steven S. Lumetta. All rights reserved.

slide 1

## Serial Design is At Least 5.5x Slower

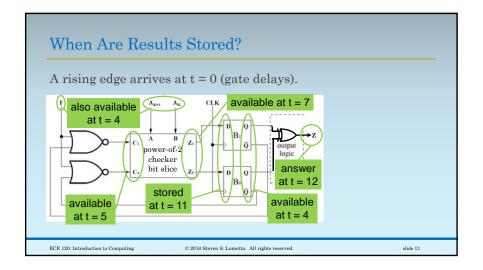

To handle N-bit operands, a bit-sliced design requires N+1 gate delays.

For a serial design,

- the clock cycle must be

at least 11 gate delays, and

- $\circ$  we must execute for N/2 cycles, so

- N-bit operands require at least 11N/2 gate delays.

The serial design is at least  $\sim 5.5x$  slower.

(And may be even slower!)

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 14