University of Illinois at Urbana-Champaign Dept. of Electrical and Computer Engineering

ECE 120: Introduction to Computing

Registers

ECE 120: Introduction to Computing

© 2016-2017 Steven S. Lumetta. All rights reserved.

slide 1

# A Register Stores a Set of Bits

Most of our representations use sets of bits: unsigned, 2's complement, floating-point, ASCII.

Even messages between bit slices often require more than one bit to convey a given meaning.

A flip-flop stores a single bit.

### A register is

- a storage element

- · composed from one or more flip-flops

- operating on a common clock.

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 2

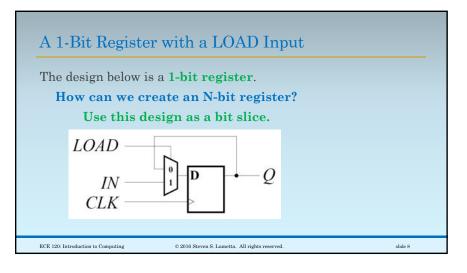

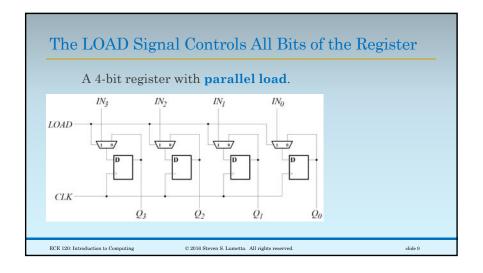

# Add an Input to Control Changing a Register's Bits

A flip-flop stores a new bit every cycle.

With registers, we want to control when the bits change value.

So we add a LOAD (or LD) input.

When LOAD = 1 on a rising clock edge, the register stores a new set of bits.

When LOAD = 0, the register retains its currently stored bits.

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 3

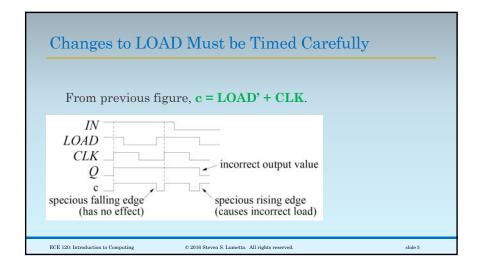

# Clock Gating Uses Extra Gates to Hide the Clock Signal

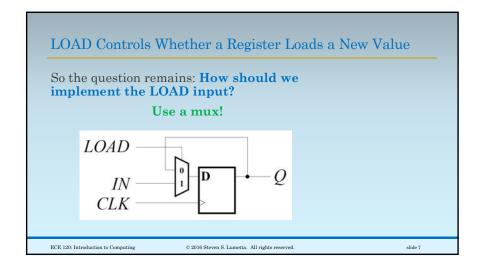

How should we implement the **LOAD** input?

The approach below may seem attractive.

It's called **clock gating**.

Generally, you should avoid this technique.

ECE 120: Introduction to Computing

$\ensuremath{\mathbb{C}}$  2016 Steven S. Lumetta. All rights reserved.

# Clock Gating Contributes to Clock Skew

More importantly,

- the extra gates in front of CLK

- ocontribute to clock skew!

So clock gating adds further complexity to the problem of distributing the clock signal to all of the flip-flops.

Except for one application (ripple counters, in a couple of weeks), you should always use and assume a common clock signal in our class (no clock gating).

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

# Simple Shift Registers Have Many Applications

For example, optical networks can transmit bits at rates above  $100 \times 10^9$  / second (100 Gbps), but CMOS clock speeds rarely exceed 4-5 GHz.

**Descrialization** (and **serialization**, **SERDES**) can be done with shift registers:

- shift into a 25-bit shift register at 100 GHz,

- then read 25 bits out in parallel at 4 GHz.

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

Shift Registers Provide Fixed Delay

My postdoc is currently working on acceleration of a particular code for computational genomics.

Data arrive from memory in a block (in a single cycle), but different parts of the data are needed in different cycles.

Solution? Use shift registers to deliver each part of the data to the computation elements in the correct cycle.

ECE 120: Introduction to Computing

slide 11

© 2016 Steven S. Lumetta. All rights reserved.

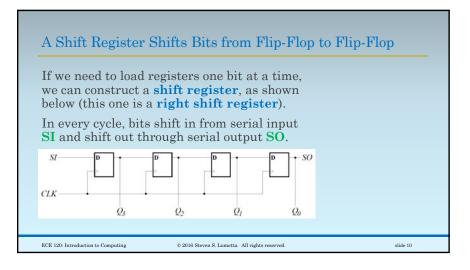

# Shift Registers Can Also Be Designed to Stop Shifting

A shift register need not shift in every cycle. Below, we use the **SHIFT** input to make the register hold its current value (**SHIFT = 0**).

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 13

# Shift Registers Also Require Fewer Wires

Serial load (shift registers) is also useful

- when wires are the limiting resource,

- as is usually the case with pins on a chip.

- Recall that parallel load of an N-bit register requires N input wires (not counting LOAD).

Examples of such applications include

- configuration of reconfigurable hardware such as Field-Programmable Gate Arrays (FPGAs, which you will use in ECE385),

- and **testing of digital systems** (shift bits in, run for a cycle, shift bits out for testing).

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 14

## Many Options for the Design of Shift Registers

direction (meaningful for some representations):

- right: from most significant bit (MSB) to least significant bit (LSB)

- **left**: from LSB to MSB.

boundaries: how to manage serial input

- exposed: input signal for serial input SI

- logical: shift in 0s (serial input)

- arithmetic: shift based on 2's complement

- cyclic: connect SO back to SI, possibly through another register (allows building of bigger shifts from smaller ones).

ECE 120: Introduction to Computing

© 2016-2017 Steven S. Lumetta. All rights reserved

slide 15

# We Can Combine Several Types

But we don't have to pick one design.

Let's build one register that performs one of four distinct operations based on control inputs  $C_1C_0$ .

| For example                             | $C_1C_0$ | meaning                                |

|-----------------------------------------|----------|----------------------------------------|

| 1                                       | 00       | retain current value                   |

| How can we build it?                    | 01       | shift left (low to high)               |

| With a mux!                             | 10       | load new value (from IN <sub>i</sub> ) |

| , i i i i i i i i i i i i i i i i i i i | 11       | shift right (high to low)              |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

# We Can Combine Several Types Each bit of the register uses a 4-to-1 mux. $Q_{i+1} Q_{i-1}$ $Q_{i-1} Q_{i-1}$ $Q_{i-1} Q_{i-1}$ $Q_{i-1} Q_{i-1}$

© 2016 Steven S. Lumetta. All rights reserved.

ECE 120: Introduction to Computing